# HY14E10/HY14E10M

**User's Guide**

**Digital Pressure Sensor Platform**

# **Table of Contents**

| 1.   | READING GUIDANCE                                          | 4  |

|------|-----------------------------------------------------------|----|

| 1.1. | Terms and Definition                                      | 5  |

| 2.   | CENTRAL PROCESSING UNIT (CPU)                             | 7  |

| 2.1. | CPU Core                                                  | 7  |

| 2.2. | Memory                                                    | 8  |

| 3.   | OSCILLATOR, CLOCK SOURCE AND POWER CONSUMPTION MANAGEMENT | 16 |

| 3.1. | Oscillator                                                | 16 |

| 3.2. | CPU and Peripheral Circuit Clock Source                   | 17 |

| 3.3. | Register Description-Operation Clock Source Controller    | 19 |

| 4.   | RESET                                                     | 20 |

| 4.1. | Reset Event Description                                   | 20 |

| 4.2. | Status Register                                           | 22 |

| 5.   | INTERRUPT                                                 | 24 |

| 5.1. | Register Description-Interrupt                            | 25 |

| 6.   | INPUT/ OUTPUT PORT (I/O)                                  | 29 |

| 6.1. | PORT Related Register Introduction                        | 29 |

| 6.2. | Register Description-PORT                                 | 30 |

| 7.   | TIMER-A (TMA)                                             | 31 |

| 7.1. | Register Description-TMA                                  | 32 |

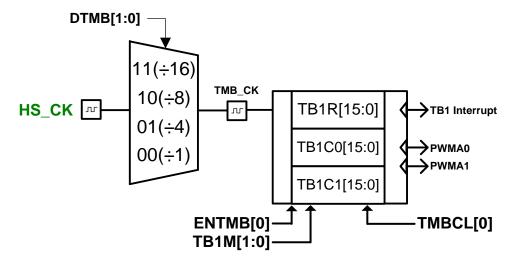

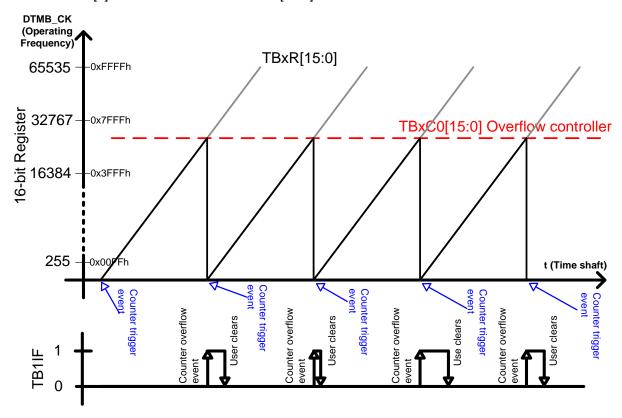

| 8.   | 16-BIT TIMERB (TMB)                                       | 33 |

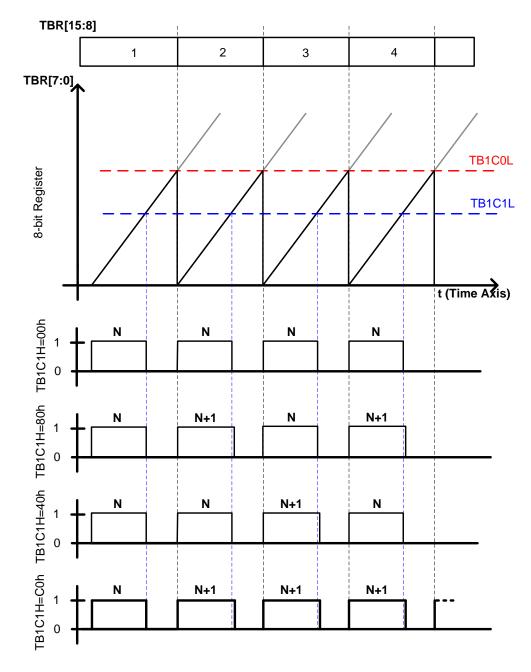

| 8.1. | 4 types of counting modes of TMB                          | 35 |

| 8.2. | TMB1 Control Register List and Instructions :             | 47 |

# **Digital Pressure Sensor Platform**

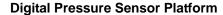

| 9.    | POWER SYSTEM(PWR)                                                       | 48  |

|-------|-------------------------------------------------------------------------|-----|

| 9.1.  | Bandgap Manual                                                          | 48  |

| 9.2.  | VDDA Manual                                                             | 49  |

| 9.3.  | Sensor Driver Manual                                                    | 49  |

| 9.4.  | ACM Manual                                                              | 49  |

| 9.5.  | LVD Manual                                                              | 49  |

| 9.6.  | Register Description-PWR                                                | 50  |

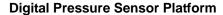

| 10.   | SIGMA DELTA ANALOG-TO-DIGITAL CONVERTER (ΣΔΑDC)                         | 52  |

| 10.1. | . ΣΔADC Manual                                                          | 54  |

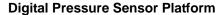

| 10.2. | . Analog Channel Input Characteristics                                  | 58  |

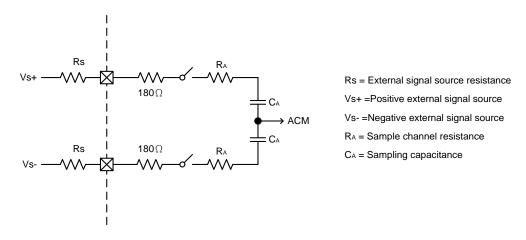

| 10.3. | . Absolute Temperature Sensor (TPS)                                     | 60  |

| 10.4. | . Register Description-ΣΔADC                                            | 62  |

| 11.   | HARDWARE MULTIPLIER                                                     | 67  |

| 11.1. | . Register Description-Hardware Multiplier                              | 67  |

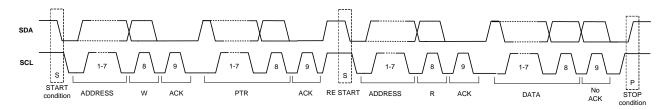

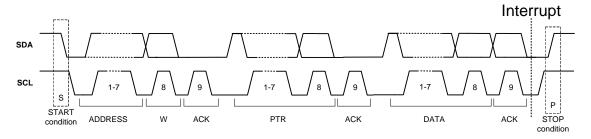

| 12.   | INTER-INTEGRATED CIRCUIT SERIAL INTERFACE (I <sup>2</sup> C)            | 68  |

| 12.1. | . Register Description- I <sup>2</sup> C Serial communication interface | 70  |

| 13.   | INFORMATION BLOCK                                                       | 72  |

| 13.1. | . System Information Block Description                                  | 73  |

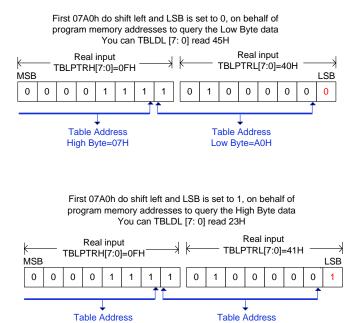

| 13.2. | . Use lookup function to read program memory                            | 73  |

| 13.3. | . Register Description- System Information Block                        | 75  |

| 14    | REVISION RECORD                                                         | 77  |

| 1 TT. |                                                                         | / / |

**Digital Pressure Sensor Platform**

# 1. Reading Guidance

#### Attention:

- HYCON Technology Corp. reserves the right to change the content of this datasheet without further notice. For most up-to-date information, please constantly visit our website: http://www.hycontek.com.

- HYCON Technology Corp. is not responsible for problems caused by figures or application circuits narrated herein whose related industrial properties belong to third parties.

- 3. Specifications of any HYCON Technology Corp. products detailed or contained herein stipulate the performance, characteristics, and functions of the specified products in the independent state. We does not guarantee of the performance, characteristics, and functions of the specified products as placed in the customer's products or equipment. Constant and sufficient verification and evaluation is highly advised.

- 4. Please note the operating conditions of input voltage, output voltage and load current and ensure the IC internal power consumption does not exceed that of package tolerance. HYCON Technology Corp. assumes no responsibility for equipment failures that resulted from using products at values that exceed, even momentarily, rated values listed in products specifications of HYCON products specified herein.

- 5. Notwithstanding this product has built-in ESD protection circuit, please do not exert excessive static electricity to protection circuit.

- 6. Products specified or contained herein cannot be employed in applications which require extremely high levels of reliability, such as device or equipment affecting the human body, health/medical equipments, security systems, or any apparatus installed in aircrafts and other vehicles.

- 7. Despite the fact that HYCON Technology Corp. endeavors to enhance product quality as well as reliability in every possible way, failure or malfunction of semiconductor products may happen. Hence, users are strongly recommended to comply with safety design including redundancy and fire-precaution equipments to prevent any accidents and fires that may follow.

- Use of the information described herein for other purposes and/or reproduction or copying without the permission of HYCON Technology Corp. is strictly prohibited.

#### 1.1. Terms and Definition

## 1.1.1. Glossary

1MW 1MegaWord

1KB 1KiloByte

ADC Analog to Digital Converter

Bit bit

BOR Brown-Out Reset

BSR Bank Select Register

Byte Byte

CCP Capture and Compare

CPU Central Processing Unit

DAC Digital-to-Analog Converter

DM Data Memory

ECAP Enhance Comparator FSR File Select Register

GPR General Purpose Register

HAO High Accuracy Oscillator

LNOP Low Noise OP AMP

LPO Low Power Oscillator

LSB Least Significant Bit

MEM Memory

MPM Main Program Memory

MSB Most Significant Bit

OTP One Time Program-EPROM

PC Program Counter

PPF PWM and PFD

ΣΔΑDC Sigma-Delta ADC

SR Special Register

SRAM Static Random Access Memory

STK Stack

WDT Watch Dog Timer WREG Work Register

© 2016 HYCON Technology Corp

UG-HY14E10-V06\_EN

# 1.1.2. Register Related Glossary

[] Register length <> Register value

ABC[7:0] ABC register had 0 to 7bit

ABC<111> ABC register had 3bit and value had 111 of binary

ABC<11x> x: can be neglected, it can be set as 1 or 0

rw Read/Write

r Read only

r0 Read as 0

r1 Read as 1

w Write only

w0 Write as 0

w1 Write as 1

h0 cleared by Hardware

h1 set by Hardware u0 cleared by User u1 set by User

- Not use

! users are forbidden to change

u unchangedx unknown

d depends on condition

© 2016 HYCON Technology Corp

UG-HY14E10-V06\_EN

**Digital Pressure Sensor Platform**

# 2. Central Processing Unit (CPU)

## 2.1. CPU Core

CPU Core (H08) adopts Harvard architecture concept in order to enhance execution efficiency. Separate program memory and data memory incorporated in program memory address increases user convenience of program writing.

#### CPU features include:

- Isolated design frame of program memory and data memory upgrades instruction execution speed and CPU efficiency.

- ♦ Max 46 operation instructions include block switching and stacking control of data memory.

- One instruction accomplished utmost 16-bit FSR register data movement and address 1MW program memory look-up-table instruction.

- Data memory operation includes Program Counter (PC), Status Register (Status) and Stack Register (Stack) data movement.

- The CPU core is H08B core of starter edition.

© 2016 HYCON Technology Corp

#### 2.2. Memory

Memory is composed by program memory (EEPROM) and data memory (SRAM). Memory size differs from diverse part number; hence product data sheets should be read with extra caution.

#### **Program Memory:**

Main Program Memory (MPM)

Program Counter (PC)

Stack (STK)

#### Data Memory:

Special Register (SR)

General Purpose Register (GPR)

**Memory Related Registers:** (x: Means it constitutes several registers)

**PC[10:0]** PCHSR[2:0],PCLATH[2:0],PCLATL[7:0]

**TOS[10:0]** TOSH[2:0],TOSL[7:0]

**FSR0[7:0]** FSR0L[7:0] **INDF0** INDF0[7:0]

STKCN STKFL,STKOV,STKUN,STKPRT[2:0]

**PSTATUS** SKERR

## 2.2.1. Program Memory

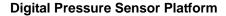

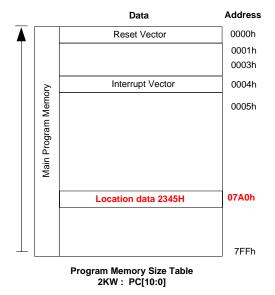

Figure 2-1 Program Memory Flame

#### 2.2.1.1. Main Program Memory, MPM

The frame of main program memory is as follows:

- Interrupt Vector Position

- ◆ Reset Vector Position

Addressing capability is from 0x00000h to 0x7FFh, with a total capacity of 2048 Word.

When the chip is not taken program writing, data type of all addresses is 1. After writing, the addresses will be 1 or 0 according to the written data type. Note: in program development, if the

© 2016 HYCON Technology Corp

assemble option of simulation software (HYIDE) has burn protection function setting, the data type of chip is 0 at the addresses that burning can be read.

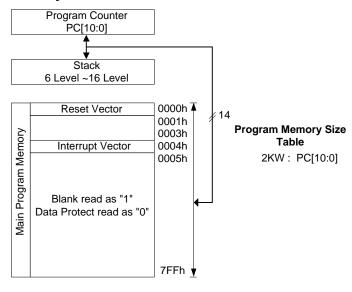

### 2.2.1.2. Program Counter (PC)

Program Counter (PC) is composed of shift register PCSR and buffer register PCLAT. Se Figure 2-2  $^{\circ}$

2KW: PC[10:0] PCLATL[7:0] PCLATH[2:0]

Figure 2-2 PC Architecture

Chip used in tool development of PC [10:0] has 11-bit data length. It is composed of two special registers, PCSRH [2:0] and PCLATL [7:0]. PCLATL [7:0] and PCLATH [2:0] can be read / written directly, while PCSRH [2:0] cannot be read / written directly and it must use buffer register PCLATH [2:0] as indirect reading /writing.

Before reading PC [10:0], it must read PCLATL [7:0] first and then read PCLATH [2:0] before reading correct data. Reverse order will not read correct data.

Before writing PC [10:0], it must write PCLATH [2:0] and then PCLATL [7:0] finally. Reverse order will not write correct data.

#### 2.2.1.3. Stack (STK)

Stack, STK is mainly composed by Stack Index Control Register (STKCN), Top-of-Stack Register (TOSx), Stack Layer Register (STKn), Stack Error Flag Bit (SKERR) and Stack Error Reset Controller (SKRST).

When the stack appears overflow and underflow, it may lead to unexpected execution results for program. When necessary, it can restart chip via setting. In program development process, it can set stack reset control bit SKRST[0]<sup>1</sup> as <1> via software setting. When stack appears underflow or overflow, it may generate reset signal and shall restart chip after the SKERR [0] is set as <1>.

- Stack Full: Configure STKFL[0] as <1>, PC[10:0] is not influenced.

- Stack Underflow: Configure STKUN[0] as <1>, PC[10:0] moves to 0x00000h, STKPRT points to 0 Level. If SKRST[0] is set as <1>, reset signal will be aroused after stack underflow and SKERR[0] may be configured as <1>, STKUN[0] will be <0>

<sup>&</sup>lt;sup>1</sup> SKRST[0] is the generated reset signal control bit of stack error. Instead of direct read or write, it only can be set by developing software at the program development stage. That is to say, whether to generate stack error reset signal must be determined at program developing stage. If reset is chosen, after IC enpowered, SKRST [0] is set as 1, the opposite situation is set as 0.

after reset.

- Stack Overflow: Configure STKOV[0] as <1>, PC[10:0] is not influened but STKPRT remains at the last layer and new values may be written in. That is to say, the lastest written-in data may be safed after stack full. If SKRST[0] is configured as <1>, reset signal may be generated after stack overflow and SKERR[0] may be set as <1>. STKOV[0] will be set as <0> after reset.

- Errot: Configure SKERR[0] as <1>, stack error occurred. If SKRST[0] is configured <1>, reset signal will be generated after stack overflow and SKERR[0] will be placed

<1>. STKUN[0] and STKOV[0] will be configured as <0> after reset.

### 2.2.1.4. Register Description-Program Memory Controller

|         | "-"no use,"*"read/write,"w"write,"r"read,"r0"only read 0,"r1"only read 1,"w0"only write 0,"w1"only write 1 |                                     |      |      |      |      |        |           |       |             |             |  |  |

|---------|------------------------------------------------------------------------------------------------------------|-------------------------------------|------|------|------|------|--------|-----------|-------|-------------|-------------|--|--|

|         | "\$"for event status,"."unimplemented bit,"x"unknown,"u"unchanged,"d"depends on condition                  |                                     |      |      |      |      |        |           |       |             |             |  |  |

| Address | File Name                                                                                                  | Bit7                                | Bit6 | Bit5 | Bit4 | Bit3 | Bit2   | Bit1      | Bit0  | A-RESET     | R/W         |  |  |

| 018h    | SKCN                                                                                                       | SKFL                                | SKUN | SKOV | -    | -    |        | SKPRT[2:0 | ]     | 000000      | u\$\$\$\$\$ |  |  |

| 01Ah    | PCLATH                                                                                                     | -                                   | -    | -    | -    | -    | PC[10] | PC[9]     | PC[8] | 0000        | 0000        |  |  |

| 01Bh    | PCLATL                                                                                                     | TL PC Low Byte for PC<7:0> 0000 000 |      |      |      |      |        |           |       | 0000 0000   | 0000 0000   |  |  |

| 02Ch    | PSTATUS                                                                                                    | POR                                 | PD   | ТО   | IDL  | RST  | SKERR  | -         | -     | \$000 \$00. | uu\$u u\$u. |  |  |

Table 2-1Program Memory Control Register

#### **STKPTR: Stack Controller Register**

| Bit    | Name        | Description                       |

|--------|-------------|-----------------------------------|

| Bit7   | STKFL       | Stack Full Flag                   |

|        |             | <1> Occurred.                     |

|        |             | <0> Not Occurred.                 |

| Bit6   | STKUN       | Stack Underflow Flag              |

|        |             | <1> Occurred.                     |

|        |             | <0> Not Occurred.                 |

| Bit5   | STKOV       | Stack Overflow Flag               |

|        |             | <1> Occurred.                     |

|        |             | <0> Not Occurred.                 |

| Bit2~0 | STKPRT[2:0] | Stack Pointer Register            |

|        |             | <111> 7th layer                   |

|        |             | <110> 6th layer                   |

|        |             |                                   |

|        |             | <000> 0 layer , TOS[10:0]=0x0000h |

PCLATH: Program Counter High Byte, PC[10:8]

PCLATL: Program Counter Low Byte, PC[7:0]

**PSTATUS: Status Register**

| Bit  | Name  | Description                      |

|------|-------|----------------------------------|

| Bit2 | SKERR | Stack Error Generated Reset Flag |

**Digital Pressure Sensor Platform**

|  | <1> Occurred.     |

|--|-------------------|

|  | <0> Not Occurred. |

© 2016 HYCON Technology Corp

### 2.2.2. Data Memory (DM)

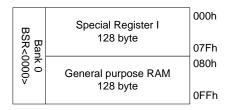

Data Memory (DM) is composed of Specially Register (SR) and General Purpose Register (GPR). Furthermore, it takes every 256byte as a block. 128byte Specially Register and 128 byte General Purpose Register is as in Figure 2-3.

Figure 2-3 Data Memory (DM) Architecture

### 2.2.2.1. Memory and Instruction

H08 instruction set can be divided A and B two version, which have great difference in memory application, such as addressing capability, hardware multiplier, table look-up instruction, support functions and parameters definition. Here just illustrate definition of instruction memory parameters. See Instruction part of Instruction Set on detailed instruction parameter illustration.

Instructions with address computation function in instruction set have three parameters at most, i.e. "f", "d" and "a".

- "f" refers to Data or Data Memory Address.

- "d" refers to data storage place after computation. If d=0, it is stored in WREG register. If d=1, it is stored in Data Memory Register.

- "a" is memory operation block appointing. If a=0, it is operated in block 0. If a=1, it is operated in BSR [3:0] appointed block.

#### 2.2.2.2. Special Register (SR)

Special Register (SR) includes CPU Core peripheral function related registers. It mainly has control function register and data return register. If it takes reading for address which is not defined in data register or address used bit, read data is 0.

In SR, it also has several registers dedicated in instruction collocation. It just introduces two kinds of commonly used registers. One is working register WREG and the other is indirect addressing register FSR. The rest special registers, which are not introduced here, will be taken detailed illustration in each chapter.

### 2.2.2.1. Working Register (WREG)

Working register is shortened as W. It is the most frequently used register for instruction collocation, ranging from data movement, computation and judgment etc.

#### 2.2.2.2. General Purpose Register (GPR)

General Purpose Register (GPR) takes data storage, computation, flag setting and other free planning area for the users.

**Digital Pressure Sensor Platform**

# 2.2.2.3. Register Description-Data Memory Controller

|      |                                                                                           |       | "-"no use," | *"read/wri | ite,"w"write," | r"read,"r0"o | nly read 0,"r | 1"only read | l 1,"w0"only v | vrite 0,"w1" | only write 1 |

|------|-------------------------------------------------------------------------------------------|-------|-------------|------------|----------------|--------------|---------------|-------------|----------------|--------------|--------------|

|      | "\$"for event status,"."unimplemented bit,"x"unknown,"u"unchanged,"d"depends on condition |       |             |            |                |              |               |             |                |              | n condition  |

| 位址   | 名稱                                                                                        | Bit 7 | Bit 6       | Bit 5      | Bit 4          | Bit 3        | Bit 2         | Bit 1       | Bit 0          | ARST         | IRST         |

| 029H | 029H WREG Working Register                                                                |       |             |            |                |              |               |             |                |              | *,*,*,*,*    |

Table 2-2 Data Memory Control Register

## **WREG: Working Register**

WREG[7:0]: See 2.2.2.2.1 Working Register, WREG Description in detail.

© 2016 HYCON Technology Corp UG-HY14E10-V06\_EN

# 2.2.3. Register List-Data Memory

| d,"d"depends on cond  | u unchange | x unknown,                                                | emented bit, | itus, . ummp    | ioi event ste   |                 |                |            |         |           |         |

|-----------------------|------------|-----------------------------------------------------------|--------------|-----------------|-----------------|-----------------|----------------|------------|---------|-----------|---------|

| R/W                   | A-RESET    | Bit0                                                      | Bit1         | Bit2            | Bit3            | Bit4            | Bit5           | Bit6       | Bit7    | File Name | Address |

| ******                | N/A        |                                                           | anged        | of FSR0 not ch  | memoryvalue     | address data    | nts of FSR0 to | Conter     |         | INDF0     | 00H     |

| -,-,-,,-,-,*          | x          |                                                           |              |                 |                 |                 |                |            |         | FSR0H     | 0FH     |

| ******                | xxxx xxxx  | Indirect Data Memory Address Pointer 0 Low Byte,FSR0[7:0] |              |                 |                 |                 |                | FSR0L      | 10H     |           |         |

| r,rw0,rw0,,r,r,r      | 000000     |                                                           | STKPRT[2:0]  |                 | -               | -               | STKOV          | STKUN      | STKFL   | STKPTR    | 18H     |

| -,-,-,- *,*,*,*       | 0000       | PC[8]                                                     | PC[9]        | PC[10]          | -               | -               | -              | -          | -       | PCLATH    | 1AH     |

| ******                | 0000 0000  |                                                           |              |                 | for PC<7:0>     | PC Low Byte     |                |            |         | PCLATL    | 1BH     |

| -,-,-,- *,*,*,*       | 0000       | TBLPTR[8]                                                 | TBLPTR[9]    | TBLPTR[10]      | TBLPTR[11]      | TBLR            | TBLR+          | TBLW       | TBLW+   | TBLPTRH   | 1DH     |

| ******                | 0000 0000  |                                                           | )            | TBLPTR<7:0>)    | ter Low Byte (  | ory Table Poin  | Program Mem    |            |         | TBLPTRL   | 1EH     |

| ******                | 0000 0000  |                                                           |              | v Byte          | able Latch Lov  | am Memory Ta    | Progr          |            |         | TBLDL     | 20H     |

| ******                | 000. 0000  | E0IE                                                      | E1IE         | LVDE            | LVD_BE          | TMAIE           | TMBIE          | ADCIE      | GIE     | INTE0     | 23H     |

| ******                | 000. 0000  | I2CW0IE                                                   | I2CW1IE      | I2CW2IE         | I2CW3IE         | I2CW4IE         | I2CW5IE        | I2CW6IE    | I2CW7IE | INTE1     | 24H     |

| ******                | 000. 0000  | I2CW8IE                                                   | I2CW9IE      | I2CW10IE        | -               | -               | -              | -          | -       | INTE2     | 25H     |

| w0                    | 000. 0000  | E0IF                                                      | E1IF         | LVDF            | LVD_BF          | TMAIF           | TMBIF          | ADCIF      | -       | INTF0     | 26H     |

| w0                    | 000. 0000  | I2CW0IF                                                   | I2CW1IF      | I2CW2IF         | I2CW3IF         | I2CW4IF         | I2CW5IF        | I2CW6IF    | I2CW7IF | INTF1     | 27H     |

| w0                    | 000.0000   | I2CW8IF                                                   | I2CW9IF      | I2CW10IF        | -               | -               | -              | -          | -       | INTF2     | 28H     |

| ******                | xxxx xxxx  | Working Register                                          |              |                 |                 |                 |                |            | WREG    | 29H       |         |

| -,-,-,* *,*,*         | x xxxx     | Z                                                         | -            | -               | -               | С               | -              | -          | -       | STATUS    | 2BH     |

| rw0,rw0,rw0,rw0 -,rw0 | 000d .0    | I2C_GC_RST                                                | I2C_RST      | SKERR           | Crst            | IDLE            | -              | PD         | BOR     | PSTATUS   | 2CH     |

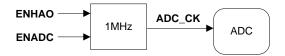

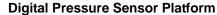

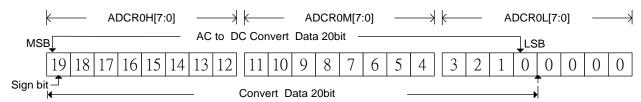

| ******                | xxxx xxxx  |                                                           |              |                 | 19:12]          | ADC[            |                |            |         | ADCR0H    | 2DH     |

| ******                | xxxx xxxx  |                                                           |              |                 | [11:4]          | ADC             |                |            |         | ADCR0M    | 2EH     |

| ******                | xxxx xxxx  | 0                                                         | 0            | 0               | 0               |                 | [3:0]          | ADC        |         | ADCR0L    | 2FH     |

| ******                | xxxx xxxx  | ADC[16]                                                   | ADC[17]      | ADC[18]         | ADC[19]         | ADC[19]         | ADC[19]        | ADC[19]    | ADC[19] | ADCR1H    | 30H     |

| ******                | xxxx xxxx  |                                                           |              |                 | [15:8]          | ADC             |                |            |         | ADCR1M    | 31H     |

| ******                | xxxx xxxx  |                                                           |              |                 | [7:0]           | ADC             |                |            |         | ADCR1L    | 32H     |

| ******                | 000. 0000  | ENADC                                                     | ENLVD        | ENLDO           | TPSLCN          | INIS            | ENSDR          | ENTPS      | ENBGR   | PWRCN0    | 33H     |

| ******                | 000. 0000  | LVDO                                                      | /[1:0]       | LDO\            | /[1:0]          | LVD\            | /[1:0]         | SDR        | ADHV    | PWRCN1    | 34H     |

| ******                | 000. 0000  | И[1:0]                                                    | SAC          | [1:0]           | ADG             | VREGN           |                | OSR[2:0]   |         | ADCCN0    | 35H     |

| ******                | 000. 0000  | [1:0]                                                     | VRI          |                 | INH[2:0]        |                 |                | INL[2:0]   |         | ADCCN1    | 36H     |

| * * * * * * * *       | 000. 0000  | ADRST                                                     | -            | -               | [1:0]           | TCR             |                | DCSET[2:0] |         | ADCCN2    | 37H     |

| ******                | 000. 0011  | ENLPO                                                     | ENHAO        | CPUCKS          | M[1:0]          | HAON            | -              | -          | -       | CLKCN     | 38H     |

| ******                | xxxx xxxx  |                                                           |              | plexer output   | / LSB for mult  | plexer input A  | LSB for multi  |            |         | AL_MO0    | 39H     |

| ******                | xxxx xxxx  |                                                           |              | iplexer output  | / 15-8 bit mult | iplexer input A | MSB for mult   |            |         | AH_MO1    | зан     |

| ******                | xxxx xxxx  |                                                           |              | tiplexer output | 23-16 bit mul   | olexer input B  | LSB for multip |            |         | BL_MO2    | звн     |

| ******                | xxxx xxxx  |                                                           |              | tiplexer output | / MSB for mul   | plexer input B  | MSB for multi  |            |         | BH_MO3    | 3CH     |

| ******                | 000. 0000  | PT0IO                                                     | TC0          | PU0             | ENPWM10         | G[1:0]          | PT0E           | -          | -       | PT0       | 3DH     |

| ******                | 000. 0000  | PT1IO                                                     | TC1          | PU1             | ENPWM00         | G[1:0]          | PT1E           | -          | -       | PT1       | 3EH     |

| ******                | 000. 0000  | PT2IO                                                     | TC2          | PU2             | ENPWM10         | -               | -              | -          | -       | PT2       | 3FH     |

| ******                | 000. 0000  | PT3IO                                                     | TC3          | PU3             | ENPWM00         | -               | -              | -          | -       | PT3       | 40H     |

Table 2-3 Data Memory List

| ly write 0,"w1"only write | read 1,"w0"o | nd 0,"r1"only | d,"r0"only rea           | "write,"r"rea | read/write,"w   | "-"no use,"*"  |        |        |        |           |           |

|---------------------------|--------------|---------------|--------------------------|---------------|-----------------|----------------|--------|--------|--------|-----------|-----------|

| ""d"depends on conditi    | "u"unchange  | "x"unknown,   | lemented bit,            | tus,"."unimp  | "for event sta  | "\$            |        |        |        |           |           |

| R/W                       | A-RESET      | Bit0          | Bit1                     | Bit2          | Bit3            | Bit4           | Bit5   | Bit6   | Bit7   | File Name | Address   |

| *****                     | 0000 0000    |               |                          |               | .AG[7:0]        | SEL_FL         |        |        |        | LSB_SEL   | 41H       |

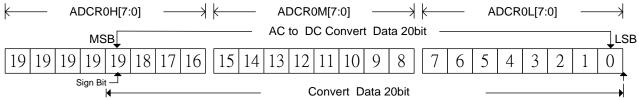

| RRRRRRRW                  | 0000 0000    | EN_SCLO       | 0                        | 0             | 0               | 0              | SP     | scu_L3 | TIP    | I2C_CMD   | 42H       |

| w                         | xxxx xxxx    |               |                          |               | tput Buffer 0   | I2C Data Ou    |        |        |        | I2C_O0    | 43H       |

| w                         | XXXX XXXX    |               |                          |               | tput Buffer 1   | I2C Data Ou    |        |        |        | I2C_O1    | 44H       |

| w                         | xxxx xxxx    |               |                          |               | tput Buffer 2   | I2C Data Οι    |        |        |        | I2C_O2    | 45H       |

| w                         | xxxx xxxx    |               |                          |               | tput Buffer 3   | I2C Data Ou    |        |        |        | I2C_O3    | 46H       |

| w                         | xxxx xxxx    |               |                          |               | tput Buffer 4   | I2C Data Οι    |        |        |        | I2C_O4    | 47H       |

| w                         | xxxx xxxx    |               |                          |               | tput Buffer 5   | I2C Data Ou    |        |        |        | I2C_O5    | 48H       |

| w                         | xxxx xxxx    |               |                          |               | tput Buffer 6   | I2C Data Ou    |        |        |        | I2C_O6    | 49H       |

| w                         | xxxx xxxx    |               |                          |               | tput Buffer 7   | I2C Data Ou    |        |        |        | I2C_07    | 4AH       |

| r                         | xxxx xxxx    |               |                          |               | put Buffer 0    | I2C Data In    |        |        |        | I2C_I0    | 4BH       |

| r                         | xxxx xxxx    |               |                          |               | put Buffer 1    | I2C Data In    |        |        |        | I2C_I1    | 4CH       |

| r                         | xxxx xxxx    |               |                          |               | put Buffer 2    | I2C Data In    |        |        |        | I2C_I2    | 4DH       |

| r                         | xxxx xxxx    |               | I2C Data Intput Buffer 3 |               |                 |                |        |        |        |           | 4EH       |

| r                         | xxxx xxxx    |               |                          |               | put Buffer 4    | I2C Data In    |        |        |        | I2C_I4    | 4FH       |

| r                         | xxxx xxxx    |               |                          |               | put Buffer 5    | I2C Data In    |        |        |        | I2C_I5    | 50H       |

| r                         | xxxx xxxx    |               |                          |               | put Buffer 6    | I2C Data In    |        |        |        | I2C_I6    | 51H       |

| r                         | xxxx xxxx    |               |                          |               | put Buffer 7    | I2C Data In    |        |        |        | I2C_I7    | 52H       |

| r                         | xxxx xxxx    |               |                          |               | put Buffer 8    | I2C Data In    |        |        |        | I2C_I8    | 53H       |

| r                         | xxxx xxxx    |               |                          |               | put Buffer 9    | I2C Data In    |        |        |        | I2C_I9    | 54H       |

| r                         | xxxx xxxx    |               |                          |               | out Buffer 10   | I2C Data Int   |        |        |        | I2C_I10   | 55H       |

| *,*,*,* rw1,*,*,*         | 0000 \$000   | -             |                          |               | DTMA[2:0]       |                | TMAS   | TMACL  | ENTMA  | TMACN     | 56H       |

| r,r,r,r r,r,r,r           | 0000 0000    |               |                          |               | R[7:0]          | TMA            |        |        |        | TMAR      | 57H       |

| ******                    | 0000 0000    | TMBCL         | -                        | -             | 3[1:0]          | DTM            | M[1:0] | TB1N   | ENTMB  | TB1CN0    | 58H       |

| * * * * * * * *           | xxxx xxxx    |               |                          | 0 [7:0]       | dition Registe  | B1 counter Cor | Timer  |        |        | TB1C0L    | 59H       |

| ******                    | XXXX XXXX    |               |                          | 0 [15:8]      | dition Register | 31 counter Con | TimerE |        |        | TB1C0H    | 5AH       |

| ******                    | xxxx xxxx    |               |                          | 1 [7:0]       | dition Registe  | B1 counter Cor | Timer  |        |        | TB1C1L    | 5BH       |

| * * * * * * * *           | xxxx xxxx    |               |                          | 1 [15:8]      | dition Register | 31 counter Con | TimerE |        |        | TB1C1H    | 5CH       |

| 0,1,1,1,1,0,0             |              | 0             | 0                        | 0             | 0               | 0              | 0      | PGM    | EN_TBL | EE_CTRL   | 5EH       |

|                           | xxxx xxxx    |               |                          | Byte          | egister as 128  | eral Purpose F | Ger    |        |        | GPR0      | 30H ~ FFH |

Table 2-4 Data Memory List (Continued)

# 3. Oscillator, Clock Source and Power Consumption Management

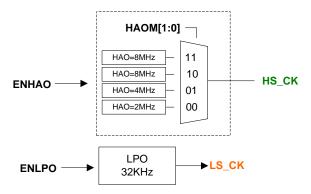

HY14E10x have two clock sources, ie HAO and LPO, as in Table 3-1. It can distribute and manage CPU and peripheral operation frequency feasibly through clock controller register. Furthermore, it can adjust power consumption of chip properly to reach the energy saving purpose.

#### **Abstract of Clock Control Register:**

CLKCN HAOM[1:0], CPUCKS ,ENHAO,ENLPO

| Symbol    | Frequency | Frequ         | uency Controller         | Instruction Execution Status |             |  |

|-----------|-----------|---------------|--------------------------|------------------------------|-------------|--|

|           |           | CLKCN         | [7:0] Configuration      |                              |             |  |

|           |           | ENHAO[0]      | HAOM[1:0]                | SLP                          | IDLE        |  |

| HAOM[1:0] | 8MHz      | 1 11          |                          | Stop                         | Oscillation |  |

|           | 8MHz      | 1 10          |                          | Stop                         | Oscillation |  |

|           | 4MHz      | 1             | 01                       | Stop                         | Oscillation |  |

|           | 2MHz      | 1             | 00                       | Stop                         | Oscillation |  |

| ENLPO     | 32KHz     | Oscillation i | s started after the chip | Stop                         | Oscillation |  |

|           |           | i:            | s power on.              |                              |             |  |

Table 3-1Internal RC Oscillator Parameter, Frequency Controller Configuration and Instruction Status

#### 3.1. Oscillator

#### 3.1.1. HAO Oscillator

HAO is internal high speed RC oscillator. Typical output frequency is 2.0~8.0MHz.

When CPU of HY14E10x products uses other oscillators as operation clock source, it can shut off the HAO oscillator via ENHAO[0] setting.

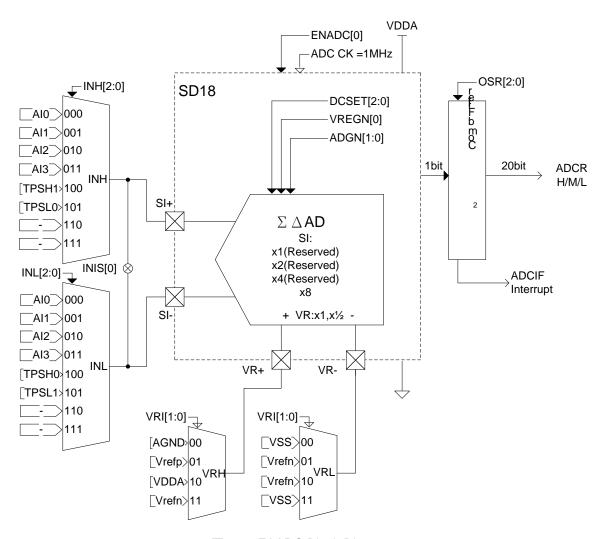

Note: SD18 sampling frequency regardless of how the choice of HAO, will be fixed frequency division to 1MHz. However, when the ADC is turned on, the HAO frequency source must select 4MHz, the ADC will be the best effect.

#### 3.1.2. LPO Oscillator

LPO is internal low speed RC oscillator. Typical output frequency is 32KHz. it is mainly applied to low speed and power saving CPU operation mode clock source.

After HY14E10x of products execute Sleep instructions, LPO oscillator is shut off. LPO will be started oscillation automatically when the chip is awakened.

### 3.2. CPU and Peripheral Circuit Clock Source

## 3.2.1. Clock Source Configuration

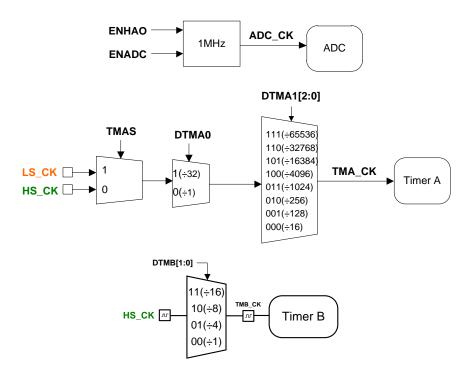

Two groups of oscillators output (HS\_CK \ LS\_CK) will be started /stopped, switched and pre-scaled frequency via pre-set operation clock distributor, and then enter CPU and all peripheral circuits of chip, as in Figure 3-1.

Figure 3-1 Pre-set operation Clock Distributor

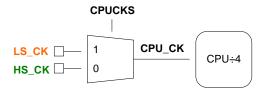

#### 3.2.2. CPU Clock Source

CPU has several operation frequency for option. Via CPUCKS[0], optional operation frequency is from HS\_CK or DHS\_CK.

Instruction operation frequency adopts 1/4 CPU\_CK design and frequency is divided to frequency source of INTR\_CK.

- When operating  $\Sigma \triangle ADC$ , it is suggested to divide current operation frequency after using HAO=4M for CPU to obtain better performance.

- When CPU\_CK frequency and instruction execute cycle, it is as in Figure 3-2.

Table 3-2 lists the relation between CPU operation frequency and instruction cycle briefly.

Figure 3-2 CPU and Peripheral Operation Clock

| Operation        | CPU       | Instruction |       |  |  |

|------------------|-----------|-------------|-------|--|--|

| Frequency CPU_CK | Frequency | Frequency   | Cycle |  |  |

| 8MHZ             | 8MHZ      | 2MHz        | 0.5us |  |  |

| 4MHz             | 4MHz      | 1MHz        | 1us   |  |  |

| 2MHz             | 2MHz      | 500kHz      | 2us   |  |  |

| 32KHz            | 32KHz     | 8KHz        | 125us |  |  |

Table 3-2 CPU Operation Frequency and Instruction Execution Cycle

### 3.2.3. CPU Peripheral Circuit Clock Source

Operation clock of HY14E10x peripheral circuits is configured by different configuration controller and frequency pre-scaler. The configuration will make detailed illustration in peripheral units, so peripheral operation clock configuration diagram is just attached here, as in Figure 3-3.

Figure 3-3 Peripheral Operation Clock Configuration Diagram

© 2016 HYCON Technology Corp

# 3.3. Register Description-Operation Clock Source Controller

|         | "-"no use,"*"read/write,"w"write,"r"read,"r0"only read 0,"r1"only read 1,"w0"only write 0,"w1"only write 1 |      |      |      |       |       |        |       |       |           |        |

|---------|------------------------------------------------------------------------------------------------------------|------|------|------|-------|-------|--------|-------|-------|-----------|--------|

|         | "\$"for event status,"."unimplemented bit,"x"unknown,"u"unchanged,"d"depends on condition                  |      |      |      |       |       |        |       |       |           |        |

| Address | File Name                                                                                                  | Bit7 | Bit6 | Bit5 | Bit4  | Bit3  | Bit2   | Bit1  | Bit0  | A-RESET   | R/W    |

| 38H     | CLKCN                                                                                                      | -    | -    | -    | HAOM1 | HAOM0 | CPUCKS | ENHAO | ENLPO | 000. 0011 | ****** |

Table 3-3 Operation Clock Source Control Register

# **CLKCN**[7:0]: Chip Operation Frequency Control Register

| Bit    | Name      | Description                                                                      |

|--------|-----------|----------------------------------------------------------------------------------|

| Bit4~3 | HAOM[1:0] | Internal Oscillator HAO Oscillation Frequency Selection                          |

|        |           | <11> 8MHz                                                                        |

|        |           | <10> 8MHz                                                                        |

|        |           | <01> 4MHz                                                                        |

|        |           | <00> 2MHz                                                                        |

| Bit2   | CPUCKS    | CPU Clock Source Selection                                                       |

|        |           | <1> Selection LS, Internal low frequency oscillator(LPO)                         |

|        |           | <0> Selection HS, Internal high-frequency oscillator(HAO)                        |

|        |           | (ADC operating frequency fixed 1MHz, HS must enable.)                            |

| Bit1   | ENHAO     | Internal HAO Oscillator Control Bit                                              |

|        |           | Sleep is invalid, ineffective BOR voltage VDD is lower than the rest are free to |

|        |           | switch.                                                                          |

|        |           | <1> Enable HAO                                                                   |

|        |           | <0> Disable HAO                                                                  |

| Bit0   | ENLPO     | Internal LPO Oscillator Control Bit                                              |

|        |           | Sleep is invalid, ineffective BOR voltage VDD is lower than the rest are free to |

|        |           | switch.                                                                          |

|        |           | <1> Enable LPO                                                                   |

|        |           | <0> Disable LPO                                                                  |

© 2016 HYCON Technology Corp UG-HY14E10-V06\_EN

#### 4. RESET

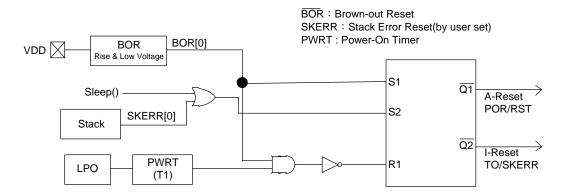

HY14E10x reset line contains the following events to trigger a reset signal, Reset block diagram is as Figure 4-1.

- ♦ BOR Power interference reset

- ◆ **SKERR** Stack error reset (determined by the user)

#### **Abstract of Operation Status Register:**

**PSTATUS** BOR, PD, IDLE, SKERR

Figure 4-1 Reset Block Diagram

These reset events can be divided into software reset and hardware reset, as in Table 4-1. CPU reset program is started by 0x0000h.

| Reset Type | Event | Sym.    | Description                                             |

|------------|-------|---------|---------------------------------------------------------|

| Hardware   | BOR   | A-RESET | CPU restart needs internal oscillator completes counter |

| Reset      |       | A-RESET | starting before entering normal operation status.       |

| Low Tier   | SKERR | I-RESET | It only clears partial register. CPU is back to normal  |

| Reset      |       | I-KESET | operation status rapidly.                               |

Table 4-1 Reset Rank List

### 4.1. Reset Event Description

#### 4.1.1. BOR Power Interference Reset

When CPU is suffered from external interference during powering on process or the power is suffered from external interference, CPU will enter into normal operation voltage from abnormal operation and low operation voltage. Therefore, if CPU cannot be in reset status when the operation voltage is too low, it may cause crash of CPU and make the operation of peripheral circuits abnormal. Therefore, it must rely on BOR circuit function. When it detects that operation voltage is suffered from interference and voltage level is lower than the designed value, it may generate reset signal and make chip enter restart status, until the operation voltage is recovered. Then it will relieve reset signal and make chip enter normal operation mode.

When BOR reset occurs, BOR[0] flag in PSTATUS[7:0] register is set as <1> to record the occurred event.

HY14E10x of BOR circuits will generate about 0.6uA power consumption. It cannot be closed via

**Digital Pressure Sensor Platform**

program or other setting method.

#### 4.1.2. SKERR Stack Error Reset

When the program occurs stack overflow or underflow, it may generate reset signal and make chip enter rapid start status. When SKERR stack error reset occurs, SKERR[0] flag in PSTATUS[7:0] register is set as <1> to record the occurred event. See *Memory* Section on detailed operation description.

© 2016 HYCON Technology Corp

## 4.2. Status Register

Chip operation status is displayed in PSTATUS[7:0] reset register. Mutual relation is as in Table 4-2  $^{\circ}$

"0": Not Occured, "1": Occurred, "u": Not Changed, "-": Not Used

| Name/Status    | Address | 7   | 6  | 5 | 4    | 3 | 2     | 1 | 0 |

|----------------|---------|-----|----|---|------|---|-------|---|---|

| PSTATUS        | 02CH    | BOR | PD | - | IDLE | - | SKERR | - | - |

| Hardware Reset | BOR     | 4   | 0  |   | 0    |   | 0     |   |   |

| (A-RESET)      | BOR     | 1   | 0  |   | 0    |   | 0     |   |   |

| Software Reset | SKERR   |     |    |   |      |   | 1     |   |   |

| (I-RESET)      | SKEKK   | R u | u  |   | u    |   | I     |   |   |

Table 4-2 Reset Status Flags Relation Table

# 4.2.1. Sequence Diagram of Reset Status

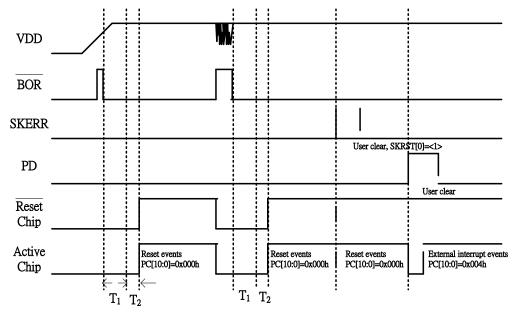

Figure 4-2 presents the time frame from hardware reset signal happened to IC accesses into operating status.

$T_1$ : 2048 LPO delay times,  $T_2$ : 1024 HAO delay times.

Figure 4-2 Sequence Diagram of Reset & Operation Mode and Status Flags

"-": no definition

| Doost Cignal | Delay            | / Time | Э  | Operating Status |         |         |  |

|--------------|------------------|--------|----|------------------|---------|---------|--|

| Reset Signal | Symbol           | T1     | T2 | Run              | Idle    | Sleep   |  |

| BOR          | t <sub>RST</sub> | T1+T2  |    | Valid            | Valid   | Valid   |  |

| SKERR        | -                | -      |    | Valid            | Invalid | Invalid |  |

Table 4-3 Interrelation of Reset Status Delay Time and Operating Status

# 4.2.2. Register Description-Reset Status

|         | "\$"for event status,"."unimplemented bit,"x"unknown,"u"unchanged,"d"depends on condition |      |      |      |      |          |       |         |            |         |                           |

|---------|-------------------------------------------------------------------------------------------|------|------|------|------|----------|-------|---------|------------|---------|---------------------------|

| Address | File Name                                                                                 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3     | Bit2  | Bit1    | Bit0       | A-RESET | R/W                       |

| 2CH     | PSTATUS                                                                                   | BOR  | PD   | -    | IDLE | ICP_Crst | SKERR | I2C_RST | I2C_GC_RST | 000d .0 | rw0,rw0,rw0,rw0 -,rw0,-,- |

Table 4-4 Reset Register

# **PSTATUS: Status Register**

| Bit  | Name  | Description                                                                         |

|------|-------|-------------------------------------------------------------------------------------|

| Bit7 | BOR   | BOR reset event flag                                                                |

|      |       | <1> Power interference reset has been occurred. It shall use RST or instruction for |

|      |       | clearing.                                                                           |

|      |       | <0>Not occurred interference reset                                                  |

| Bit6 | PD    | SLEEP event flag                                                                    |

|      |       | <1> Sleep event has been occurred. It shall use BOR, RST or instruction for         |

|      |       | clearing.                                                                           |

|      |       | <0> Not occurred sleep event                                                        |

| Bit4 | IDLE  | Standby IDLE event flag                                                             |

|      |       | <1> IDLE event has been occurred. It shall use BOR or instruction for clearing.     |

|      |       | <0> Not occurred IDLE event                                                         |

| Bit2 | SKERR | Stack error reset flag                                                              |

|      |       | <1> Stack error. It shall use BOR or instruction for clearing.                      |

|      |       | <0> No stack error                                                                  |

© 2016 HYCON Technology Corp UG-HY14E10-V06\_EN

# 5. Interrupt

Interrupt is composed of interrupt start controller INTE and interrupt event flag INTF. When Interrupt service is established, if it appears interrupt event, program counter (PC) will jump to interrupt address 0x0004h in PM to execute interrupt service program.

## **Abstract of Interrupt Control Register:**

| INTE0 | GIE, ADCIE, TMBIE, TMAIE, LVD_BE,L VDE, E1IE, E0IE                     |

|-------|------------------------------------------------------------------------|

| INTE1 | I2CW7IE, I2CW6IE, I2CW5IE, I2CW4IE, I2CW3IE, I2CW2IE, I2CW1IE, I2CW0IE |

| INTE2 | I2CW10, I2CW9, I2CW8IE                                                 |

| INTF0 | ADCIF, TMBIF, TMAIF, LVD_BF, LVDF, E1IF, E0IF                          |

| INTF1 | I2CW7IF, I2CW6IF, I2CW5IF, I2CW4IF, I2CW3IF, I2CW2IF, I2CW1IF, I2CW0IF |

| INTF2 | I2CW10, I2CW9, I2CW8IF                                                 |

Interrupt service event governor has two layers totally. The higher layer is interrupt service event controller GIE [0] and the lower layer is interrupt event start control bit.

- To start interrupt event, it only needs to set the controller of corresponding interrupt event start controller INTEx [7:0] as <1>. On the contrary, it will close the interrupt event when it is set as <0>.

- To start interrupt service, it only needs to set the interrupt service controller GIE[0] of interrupt control register INTE0[7:0] as <1>. On the contrary, it will close the interrupt service when it is set as <0>.

When entering into interrupt service vector, GIE [0] will be set as <0> automatically. When it is going to return interrupt occurrence address after completing interrupt service program execution, it can execute interrupt return instruction RETI directly. At the moment, GIE [0] will be set as <1> automatically. Or it executes return instruction RET, and GIE [0] status maintains at 0 at the moment.

# 5.1. Register Description-Interrupt

|         |                                                                                           |         | "-"no use,"*" | read/writ | e,"w"write," | r"read,"r0"o | nly read 0," | 1"only read | 1,"w0"only | write 0,"w1 | only write 1 |

|---------|-------------------------------------------------------------------------------------------|---------|---------------|-----------|--------------|--------------|--------------|-------------|------------|-------------|--------------|

|         | "\$"for event status,"."unimplemented bit,"x"unknown,"u"unchanged,"d"depends on condition |         |               |           |              |              |              |             |            |             |              |

| Address | File Name                                                                                 | Bit7    | Bit6          | Bit5      | Bit4         | Bit3         | Bit2         | Bit1        | Bit0       | A-RESET     | R/W          |

| 23H     | INTE0                                                                                     | GIE     | ADCIE         | TMBIE     | TMAIE        | LVD_BE       | LVDE         | E1IE        | EOIE       | 000. 0000   | ******       |

| 24H     | INTE1                                                                                     | I2CW7IE | I2CW6IE       | I2CW5IE   | I2CW4IE      | I2CW3IE      | I2CW2IE      | I2CW1IE     | I2CW0IE    | 000. 0000   | ******       |

| 25H     | INTE2                                                                                     | -       | -             | -         | -            | -            | I2CW10IE     | I2CW9IE     | I2CW8IE    | 000. 0000   | ******       |

| 26H     | INTF0                                                                                     | -       | ADCIF         | TMBIF     | TMAIF        | LVD_BF       | LVDF         | E1IF        | EOIF       | 000. 0000   | w 0          |

| 27H     | INTF1                                                                                     | I2CW7IF | I2CW6IF       | I2CW5IF   | I2CW4IF      | I2CW3IF      | I2CW2IF      | I2CW1IF     | I2CW0IF    | 000. 0000   | w 0          |

| 28H     | INTF2                                                                                     | -       | -             | -         | -            | -            | I2CW10IF     | I2CW9IF     | I2CW8IF    | 000. 0000   | w 0          |

Table5-1 Interrupt Register

# INTE0 : Interrupt Enable Control Register 0

| Bit  | Name   | Description                                                |

|------|--------|------------------------------------------------------------|

| Bit7 | GIE    | Global Interrupt Enable Controller                         |

|      |        | <1> Enable GIE                                             |

|      |        | <0> Disable GIE                                            |

| Bit6 | ADCIE  | ADC Interrupt Event Enable Controller                      |

|      |        | <1> Enable (Analog Digital Converter, ΣΔΑDC)               |

|      |        | <0> Disable                                                |

| Bit5 | TMBIE  | Timer-B Interrupt Event Enable Controller                  |

|      |        | <1> Enable (Timing/ Timer B, TMB)                          |

|      |        | <0> Disable                                                |

| Bit4 | TMAIE  | Timer-A Interrupt Event Enable Controller                  |

|      |        | <1> Enable (Timing/ Timer A, TMA)                          |

|      |        | <0> Disable                                                |

| Bit3 | LVD_BE | VDD Voltage Recovery Detection Interrupt Enable Controller |

|      |        | <1> Enable (VDD>LVD Interrupt)                             |

|      |        | <0> Disable                                                |

| Bit2 | LVDE   | VDD Low Voltage Detection Interrupt Enable Controller      |

|      |        | <1> Enable (VDD <lvd interrupt)<="" td=""></lvd>           |

|      |        | <0> Disable                                                |

| Bit1 | E1IE   | Input Pin 0 Interrupt Event Enable Controller              |

|      |        | <1> Enable (External Input Pin, PT1)                       |

|      |        | <0> Disable                                                |

| Bit0 | EOIE   | Input Pin 0 Interrupt Event Enable Controller              |

|      |        | <1> Enable (External Input Pin, PT0)                       |

|      |        | <0> Disable                                                |

© 2016 HYCON Technology Corp

# INTE1: Interrupt Enable Control Register 1

| Bit  | Name    | Description                                                                                     |

|------|---------|-------------------------------------------------------------------------------------------------|

| Bit7 | I2CW7IE | I <sup>2</sup> C data written to the interrupt controller to enable event                       |

|      |         | <1> Enable,(Data written to allow I <sup>2</sup> C master Buffer 7 generate an interrupt event) |

|      |         | <0> Disable                                                                                     |

| Bit6 | I2CW6IE | I <sup>2</sup> C data written to the interrupt controller to enable event                       |

|      |         | <1> Enable,(Data written to allow I <sup>2</sup> C master Buffer 6 generate an interrupt event) |

|      |         | <0> Disable                                                                                     |

| Bit5 | I2CW5IE | I <sup>2</sup> C data written to the interrupt controller to enable event                       |

|      |         | <1> Enable,(Data written to allow I <sup>2</sup> C master Buffer 5 generate an interrupt event) |

|      |         | <0> Disable                                                                                     |

| Bit4 | I2CW4IE | I <sup>2</sup> C data written to the interrupt controller to enable event                       |

|      |         | <1> Enable,(Data written to allow I <sup>2</sup> C master Buffer 4 generate an interrupt event) |

|      |         | <0> Disable                                                                                     |

| Bit3 | I2CW3IE | I <sup>2</sup> C data written to the interrupt controller to enable event                       |

|      |         | <1> Enable,(Data written to allow I <sup>2</sup> C master Buffer 3 generate an interrupt event) |

|      |         | <0> Disable                                                                                     |

| Bit2 | I2CW2IE | I <sup>2</sup> C data written to the interrupt controller to enable event                       |

|      |         | <1> Enable,(Data written to allow I <sup>2</sup> C master Buffer 2 generate an interrupt event) |

|      |         | <0> Disable                                                                                     |

| Bit1 | I2CW1IE | I <sup>2</sup> C data written to the interrupt controller to enable event                       |

|      |         | <1> Enable,(Data written to allow I <sup>2</sup> C master Buffer 1 generate an interrupt event) |

|      |         | <0> Disable                                                                                     |

| Bit0 | I2CW0IE | I <sup>2</sup> C data written to the interrupt controller to enable event                       |

|      |         | <1> Enable,(Data written to allow I <sup>2</sup> C master Buffer 0 generate an interrupt event) |

|      |         | <0> Disable                                                                                     |

# **INTE2: Interrupt Enable Control Register 2**

| Bit  | Name     | Description                                                                                     |

|------|----------|-------------------------------------------------------------------------------------------------|

| Bit2 | I2CW10IE | I <sup>2</sup> C data written to the interrupt controller to enable event                       |

|      |          | <1> Enable,(Data written to allow I <sup>2</sup> C master Buffer 10 generate an interrupt       |

|      |          | event)                                                                                          |

|      |          | <0> Disable                                                                                     |

| Bit1 | I2CW9IE  | I <sup>2</sup> C data written to the interrupt controller to enable event                       |

|      |          | <1> Enable,(Data written to allow I <sup>2</sup> C master Buffer 9 generate an interrupt event) |

|      |          | <0> Disable                                                                                     |

| Bit0 | I2CW8IE  | I <sup>2</sup> C data written to the interrupt controller to enable event                       |

|      |          | <1> Enable,(Data written to allow I <sup>2</sup> C master Buffer 8 generate an interrupt event) |

|      |          | <0> Disable                                                                                     |

# INTF0: Interrupt Event Flag Register 0

| Bit  | Name   | Description                                         |

|------|--------|-----------------------------------------------------|

| Bit6 | ADCIF  | ADC interrupt event flag                            |

|      |        | <1> Happened (Analog-to-digital converter, ΣΔΑDC)   |

|      |        | <0> Not happened                                    |

| Bit5 | TMBIF  | Timer-B interrupt event flag                        |

|      |        | <1> Happened (Time B, TMB)                          |

|      |        | <0> Not happened                                    |

| Bit4 | TMAIF  | Timer-A interrupt event flag                        |

|      |        | <1> Happened (Time A, TMA)                          |

|      |        | <0> Not happened                                    |

| Bit3 | LVD_BF | VDD voltage recovery detection interrupt event flag |

|      |        | <1> Happened (Response VDD>LVD)                     |

|      |        | <0> Not happened                                    |

| Bit2 | LVDF   | VDD Low voltage detect interrupt event flag         |

|      |        | <1> Happened (Response VDD <lvd)< td=""></lvd)<>    |

|      |        | <0> Not happened                                    |

| Bit1 | E1IF   | Interrupt event flag of input pin 1                 |

|      |        | <1> Happened (External input pin, PT1)              |

|      |        | <0> Not happened                                    |

| Bit0 | E0IF   | Interrupt event flag of input pin 0                 |

|      |        | <1> Happened (External input pin, PT0)              |

|      |        | <0> Not happened                                    |

## INTF1: Interrupt Event Flag Register 1

| Bit  | Name    | Description                                              |  |  |  |  |  |  |

|------|---------|----------------------------------------------------------|--|--|--|--|--|--|

| Bit7 | I2CW7IF | I <sup>2</sup> C data write interrupt event flag         |  |  |  |  |  |  |

|      |         | <1> Happened (I <sup>2</sup> C host write data Buffer 7) |  |  |  |  |  |  |

|      |         | <0> Not happened                                         |  |  |  |  |  |  |

| Bit6 | I2CW6IF | I <sup>2</sup> C data write interrupt event flag         |  |  |  |  |  |  |

|      |         | <1> Happened (I <sup>2</sup> C host write data Buffer 6) |  |  |  |  |  |  |

|      |         | <0> Not happened                                         |  |  |  |  |  |  |

| Bit5 | I2CW5IF | I <sup>2</sup> C data write interrupt event flag         |  |  |  |  |  |  |

|      |         | <1> Happened (I <sup>2</sup> C host write data Buffer 5) |  |  |  |  |  |  |

|      |         | <0> Not happened                                         |  |  |  |  |  |  |

| Bit4 | I2CW4IF | I <sup>2</sup> C data write interrupt event flag         |  |  |  |  |  |  |

|      |         | <1> Happened (I <sup>2</sup> C host write data Buffer 4) |  |  |  |  |  |  |

|      |         | <0> Not happened                                         |  |  |  |  |  |  |

| Bit  | Name    | Description                                              |  |  |  |  |  |  |

|------|---------|----------------------------------------------------------|--|--|--|--|--|--|

| Bit3 | I2CW3IF | I <sup>2</sup> C data write interrupt event flag         |  |  |  |  |  |  |

|      |         | <1> Happened (I <sup>2</sup> C host write data Buffer 3) |  |  |  |  |  |  |

|      |         | <0> Not happened                                         |  |  |  |  |  |  |

| Bit2 | I2CW2IF | I <sup>2</sup> C data write interrupt event flag         |  |  |  |  |  |  |

|      |         | <1> Happened (I <sup>2</sup> C host write data Buffer 2) |  |  |  |  |  |  |

|      |         | <0> Not happened                                         |  |  |  |  |  |  |

| Bit1 | I2CW1IF | I <sup>2</sup> C data write interrupt event flag         |  |  |  |  |  |  |

|      |         | <1> Happened (I <sup>2</sup> C host write data Buffer 1) |  |  |  |  |  |  |

|      |         | <0> Not happened                                         |  |  |  |  |  |  |

| Bit0 | I2CW0IF | I <sup>2</sup> C data write interrupt event flag         |  |  |  |  |  |  |

|      |         | <1> Happened (I <sup>2</sup> C host write data Buffer 0) |  |  |  |  |  |  |

|      |         | <0> Not happened                                         |  |  |  |  |  |  |

# INTF2: Interrupt Event Flag Register 2

| Bit  | Name     | Description                                               |  |  |  |  |  |  |

|------|----------|-----------------------------------------------------------|--|--|--|--|--|--|

| Bit2 | I2CW10IF | I <sup>2</sup> C data write interrupt event flag          |  |  |  |  |  |  |

|      |          | <1> Happened (I <sup>2</sup> C host write data Buffer 10) |  |  |  |  |  |  |

|      |          | <0> Not happened                                          |  |  |  |  |  |  |

| Bit1 | I2CW9IF  | I <sup>2</sup> C data write interrupt event flag          |  |  |  |  |  |  |

|      |          | <1> Happened (I <sup>2</sup> C host write data Buffer 9)  |  |  |  |  |  |  |

|      |          | <0> Not happened                                          |  |  |  |  |  |  |

| Bit0 | I2CW8IF  | I <sup>2</sup> C data write interrupt event flag          |  |  |  |  |  |  |

|      |          | <1> Happened (I <sup>2</sup> C host write data Buffer 8)  |  |  |  |  |  |  |

|      |          | <0> Not happened                                          |  |  |  |  |  |  |

# 6. Input/ Output Port (I/O)

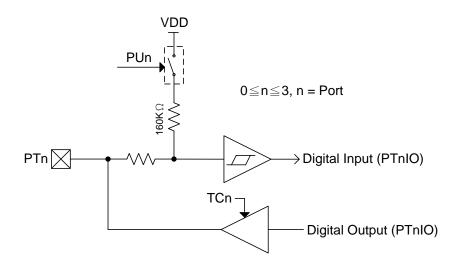

Every pins of Input/ Output Port (I/O) are one port. It can be taken as digital input and output and analog signal measuring channel. Each port is controlled by a group of registers.

#### Abstract of I/O related register:

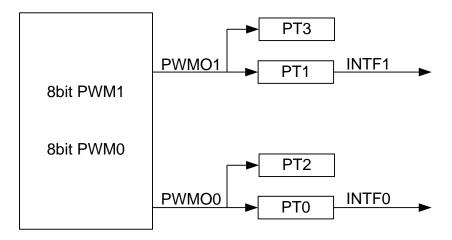

PT0 PT0GE[1:0], ENPWM0O, PU0, TC0, PT0IO

PT1 PT1GE[1:0], ENPWM1O, PU1, TC1, PT1IO

PT2 ENPWM2O, PU2, TC2, PT2IO

PT3 ENPWM3O, PU3, TC3, PT3IO

Figure 6-1 I/O Architecture Block Diagram

#### 6.1. PORT Related Register Introduction

PORT mainly offers digital or analog signal I/O pin.

#### 6.1.1. PTEG Interrupt Signal Generated Conditions

When I/O external input potential belongs to certain changes, it may cause interrupt signal. Potential changes can be divided into rising edge  $(0\rightarrow1)$  change, falling edge  $(1\rightarrow0)$  change and potential transition  $(0\rightarrow1$ or  $1\rightarrow0)$ .

#### 6.1.2. PTPU Pull-Up Resistor Control Register

When I/O is set as whether pull-up resistor function is started. Set <1> as I/O starting and set <0> as disconnection. Before the chip enters into sleep mode, if I/O is set as digital input status and external circuit connection way may cause floating phenomena of I/O, it can start pull-up resistor to avoid I.O floating and causing the chip entering into sleep mode and producing current leakage.

#### 6.1.3. TC Input/Output Control Register

When I/O is selected as input or output, set <1>I/O as output status and <0> as input status. When I/O is set as input status, it must give definite input potential when the chip enters into sleep status. Don't make I/O in floating status to avoid causing power leakage phenomena of chip.

## 6.1.4. PTIO Status Control Register

When I/O is set as input, it can read current I/O status at corresponding register position. I/O

input is high potential when the reading is 1 at the moment, and low potential when is 0.

When I/O is set as output, it can control output status at corresponding register position. I/O output is high potential when it is set as <1> at the moment, and low potential when is<0>.

# 6.2. Register Description-PORT

| "-"no use,"*"read/write,"w"write,"r"read,"r0"only read 0,"r1"only read 1,"w0"only write 0,"w1"only write 1 |                                                                                           |      |      |      |         |         |      |      |       |           |                 |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|---------|---------|------|------|-------|-----------|-----------------|

|                                                                                                            | "\$"for event status,"."unimplemented bit,"x"unknown,"u"unchanged,"d"depends on condition |      |      |      |         |         |      |      |       |           |                 |

| Address                                                                                                    | File Name                                                                                 | Bit7 | Bit6 | Bit5 | Bit4    | Bit3    | Bit2 | Bit1 | Bit0  | A-RESET   | R/W             |

| 3DH                                                                                                        | PT0                                                                                       | -    | -    | PTC  | EG[1:0] | ENPWM10 | PU0  | TC0  | PT0IO | 000. 0000 | * * * * * * * * |

| 3EH                                                                                                        | PT1                                                                                       | -    | -    | PT1  | EG[1:0] | ENPWM00 | PU1  | TC1  | PT1IO | 000. 0000 | * * * * * * * * |

| 3FH                                                                                                        | PT2                                                                                       | -    | -    | -    | -       | ENPWM10 | PU2  | TC2  | PT2IO | 000. 0000 | * * * * * * * * |

| 40H                                                                                                        | PT3                                                                                       | -    | -    | -    | -       | ENPWM00 | PU3  | TC3  | PT3IO | 000. 0000 | * * * * * * * * |

Table 6-1 PORT Control Register

# INTE0/INTF0 : Please refer to *Interrupt* Chapter PT0/ PT1/PT2/PT3 : PORT Control Register

| Bit    | Name       | Description                                                                      |  |  |  |  |  |  |

|--------|------------|----------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit5~4 | PTnGE[1:0] | Pin PTn interrupt way controller (n=0~1)                                         |  |  |  |  |  |  |

|        |            | <11> When the next CPU instruction read I/O status, when external changes to     |  |  |  |  |  |  |

|        |            | the I/O status interrupt occurs.                                                 |  |  |  |  |  |  |

|        |            | <10> potential transition (0→1 or 1→0),i.e. Producing interrupt event; interrupt |  |  |  |  |  |  |

|        |            | event will be occurred so long as potential transition.                          |  |  |  |  |  |  |

|        |            | <01> rising edge (0→1)                                                           |  |  |  |  |  |  |

|        |            | <00> falling edge (1→0)                                                          |  |  |  |  |  |  |

| Bit3   | ENPWMnO    | PWM Output control bit (0≤n≤1)                                                   |  |  |  |  |  |  |

|        |            | <1> Enable                                                                       |  |  |  |  |  |  |

|        |            | <0> Disable                                                                      |  |  |  |  |  |  |

| Bit2   | PUn        | External pin pull-up resistor control bit (0≦n≦3)                                |  |  |  |  |  |  |

|        |            | <1> Enable                                                                       |  |  |  |  |  |  |

|        |            | <0> Disable                                                                      |  |  |  |  |  |  |

| Bit1   | TCn        | External pin input /output control bit (0≦n≦3)                                   |  |  |  |  |  |  |

|        |            | <1> Enable Output Mode                                                           |  |  |  |  |  |  |

|        |            | <0> Input Mode Only                                                              |  |  |  |  |  |  |

| Bit0   | PTnIO      | External pin control bit (0≤n≤3)                                                 |  |  |  |  |  |  |

|        |            | <1> High potential                                                               |  |  |  |  |  |  |

|        |            | <0> Low potential                                                                |  |  |  |  |  |  |

# 7. Timer-A (TMA)

Timer-A (hereinafter referred to as TMA) is designed in 8-bit frame. TMA can function in Run Mode and Idle Mode.

- Ascending counter

- ◆ 4-step overflow value select

- Overflow generated interrupt event

- Counter value is readable

#### **TMA Registers:**

TMACN ENTMA, TMACL, TMAS, DTMA1[2:0]

TMAR TMAR[7:0]INTEO TMAIEINTFO TMAIF

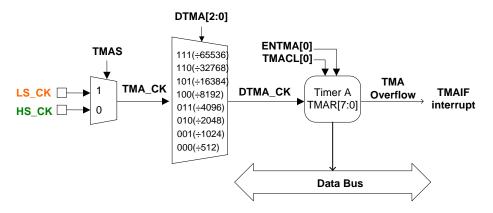

Figure 7-1 Timer-A Block Diagram

#### Operation Instructions :

Set ENTMA[0] as <1> to start TMA; on the contrary, set as<0> to close and clear TMAR[7:0].

When DTMA[2:0] timing condition is established, it may produce interrupt event and make TMAR[7:0] progressively increase 1.

TMA interrupt event TMAIF[0] must have interrupt service when TMAIE[0] is set as <1> and GIE[0] is set as <1>. TMA interruption in Debug Mode, the interrupt flag TMAI always 0. But interrupt function still exists, the user still needs to be cleared in the interrupt subroutine interrupt flag TMAIF.

Reading TMAR[7:0] will not make TMA timer zeroed.

After the user sets TMACL[0] as <1> and clear all timers of TMA, TMACL[0]will be set as <0> automatically.

TMAR[7:0] can read TMA progressively increased value of the timer, and can write motion to clear the timing value of TMAR[7:0].

# 7.1. Register Description-TMA

| "-"no use,"*"read/write,"w"write,"r"read,"r0"only read 0,"r1"only read 1,"w0"only write 0,"w1"only write 1 |                                                                                           |           |        |       |            |        |            |                    |                 |           |        |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------|--------|-------|------------|--------|------------|--------------------|-----------------|-----------|--------|